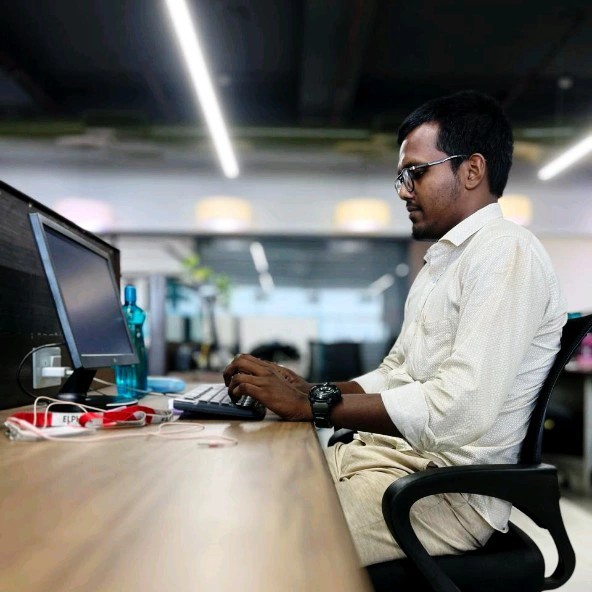

“I'm excited to announce that I recently completed a certification in Cyber Security and Ethical Hacking in January 2023. This accomplishment, during my first internship at Coincent.ai, has been a fantastic experience. I'm now eager to expand my skills into Mobile App and Back-end Development. This journey has provided me with valuable insights and inspiration to seek new challenges and network with professionals in the field.”